ナノインプリントは、ナノメートル単位の非常に微細なパターンが刻まれた「型」を押し付け、対象物に微細なパターンを形成する加工方法です。2023年10月にキヤノンが半導体向けのナノインプリント装置をリリースしたことで、注目が集まっています(同社のリリース参照)。

本記事では、次世代の半導体製造プロセスである「2nmプロセス」にナノインプリント装置が対応できるのかをテーマに、現状のハードルと関連企業の動向を整理します。現在、2nmプロセス開発で主流となっているEUV露光との比較分析に加え、TSMCなど開発をリードする企業の動向も紹介します。半導体微細化の限界に挑む企業の最先端を理解したい方は、ぜひご参照ください。

※ナノインプリント技術の全体像は以下の記事で詳しく解説しています。

【図解】ナノインプリント実用化の最前線 ~用途ごとの装置メーカーの動向と、打倒EUVに向けて限界を超えるキヤノン・キオクシアの技術

.png)

3nmプロセスから2nmプロセスへの変化(『イノベーション四季報【2022年冬号】』より)

まずは背景情報として、「2nmプロセス」の定義と、開発を進める企業の動向を解説します。

「2nmプロセス」や「3nmプロセス」といった言葉は、半導体チップ製造技術の世代を示す用語です。世代が進むほど、チップ上に描かれた回路のパターンが細かくなります。ただ、名称と実際のサイズは一致しておらず、電気電子学会(IEEE)が2021年に発行した資料によると、2nmプロセスのゲート電極(※)の幅は約14nmと推定されています。

半導体チップ微細化の最先端を走るのが台湾企業のTSMCで、2022年に3nmプロセス(2nmプロセスの1つ前の世代)のチップ量産化に成功しています。同社の2022年度のAnnual Reportによると、3nmプロセスでは上図のように「FinFET」と呼ばれる構造が採用されています。

TSMCは2nmプロセスの量産化を2025年に予定しており、チップの構造はFinFETから上図右の「GAA(Gate All Around)」と呼ばれる構造になるようです。GAAはナノシートと呼ばれる電極が積層された構造で、FinFETよりも配線の密度を高めることが可能です。TSMC以外にも、インテルやサムスン電子が2nmプロセスの量産化に向けてGAAの開発を進めています。

いずれの企業も、2nmプロセスの配線パターン作成にはオランダのASML社のEUV露光装置を使っています。現時点ではナノインプリントは採用されていないようです。

※ゲート電極:チップ上のトランジスタの、電流のON/OFF制御に使われる電極

※TSMCの経営戦略は以下の記事で解説しています。

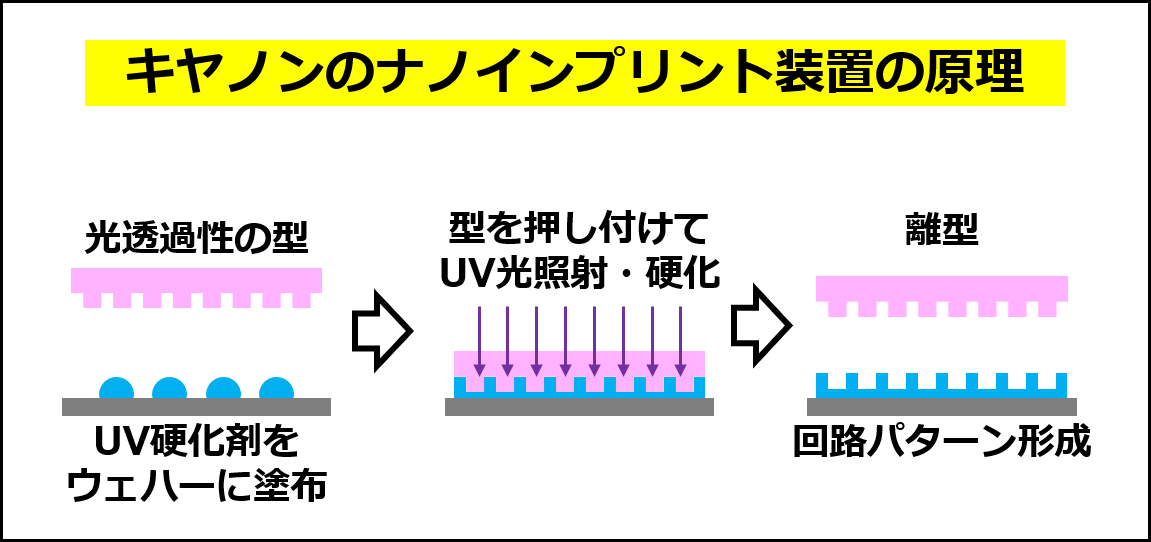

キヤノンのUV方式のナノインプリント装置の原理

続いて、キヤノンがリリースしたナノインプリント装置の概要を説明します。

上図のように、キヤノンの装置は紫外光(UV)を照射して材料を硬化させるUV方式を採用しています。ナノサイズの回路パターンが掘り込まれた「型(マスク)」をウェハーに押し付けた状態で硬化させ、型を引きはがして回路パターンを形成します。ハンコを押して文字を転写するのと同様のシンプルな原理で、マスクに描かれたパターンがウェハーに転写されます。

原理はシンプルですが、ナノレベルの微細なパターンを転写するのは非常に困難です。キヤノンは実用化のハードルを超えるために、例えば以下の工夫をしています(同社のHP参照)。

これらの工夫によりキヤノンの装置は半導体製造に使えるレベルの精度を達成し、フラッシュメモリ製造などで量産の検証が進められています。2023年10月のキヤノンのリリースによると、すでに5nmプロセスに対応した線幅の回路パターン形成は実用レベルに達しているようです。

先述の通り、現時点では2nmプロセスの開発に使われているのはEUV露光装置ですが、将来的にはナノインプリント装置も利用される可能性があります。次項ではナノインプリントによる2nmプロセス達成の実現性を評価するため、現状の課題を整理します。

※EUV露光装置の詳細は以下の記事で解説しています。

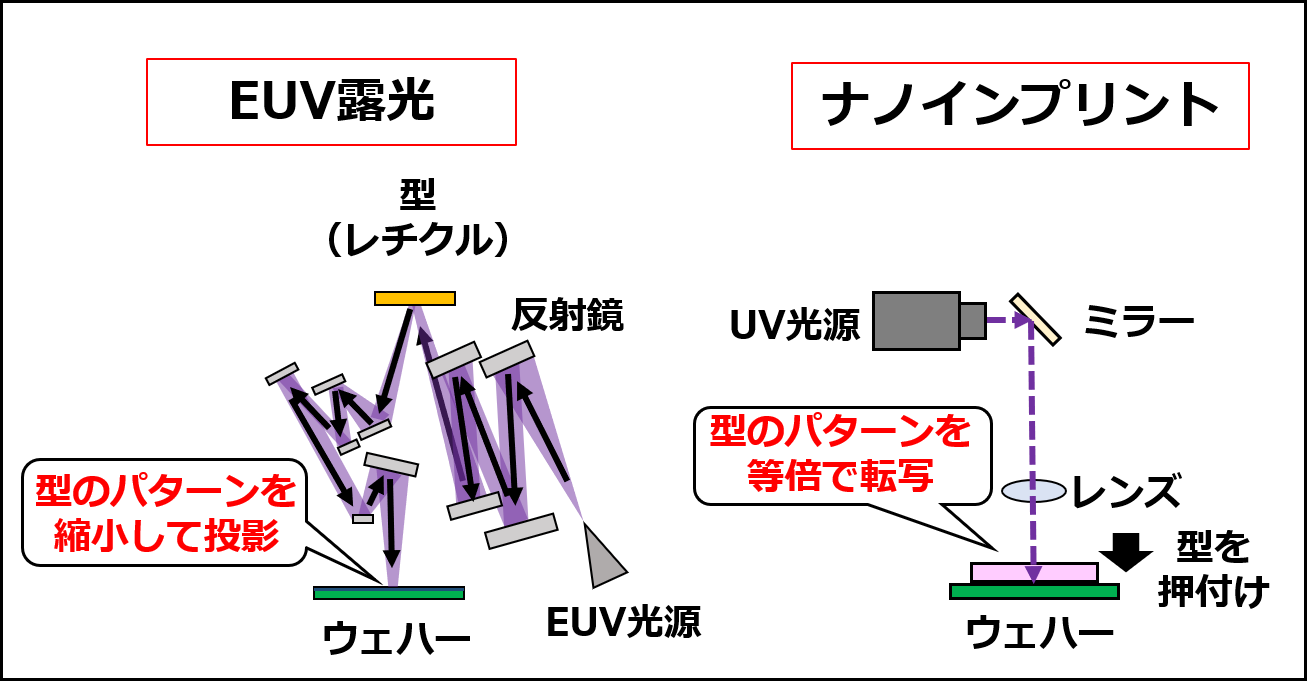

EUV露光装置とナノインプリント装置の比較

まず、EUV露光と比較したナノインプリントの技術的な課題を解説します。

上図はEUV露光装置とナノインプリント装置の内部構造の概略を示しています。ASMLのEUV露光装置は、光源から照射された光を反射させ、レチクルと呼ばれる型に描かれたパターンをウェハーに投影します。光学的に縮小して投影されるので、型に描かれたパターンよりも細かいパターンをウェハーに投影することが可能です。

一方、ナノインプリントは先述の通り型を直接ウェハーに押し付けるので、ウェハーに形成されるパターンの細かさは型と同じです。よって、EUV露光装置よりも型に描くパターンを細かくする必要があり、そこに特有の技術的ハードルがあります。

ナノインプリントの型は電子線を使った描画装置により製造されており、「型の製造技術を2nmプロセスに対応できるレベルまで進化できるか?」がひとつの重要なテーマになります。また、耐久性のある型の材料や、微細なパターンを安定して形成できるUV硬化剤の開発も並行して進める必要があります。

また、仮にナノインプリントによってEUV露光と同レベルの微細なパターンを形成できたとしても、量産化においては「前後の工程も含めた品質の検証」が必要になります。

2013年7月の日経クロステックの記事を見ると、TSMCは2013年には既にASMLのEUV露光装置を最初に導入しています。その後、EUVが量産フェーズに入るまで5年以上かかっているので、ナノインプリントも量産に使われるまでにはタイムラグがあることが予想されます。

ちなみに筆者はTSMCの工場で製造プロセスの検証に関わった経験があります。実際にその製造装置が使えるかどうかの見極めには、チップ製造プロセス全体を通しての検証が必要になります。EUVとナノインプリントでは利用する材料も異なるので、ナノインプリント工程がうまくいっても、その後の工程で材料の違い等による不具合が生じる可能性があります。

例えば、回路パターンを形成した後は、余分な材料を除去する洗浄工程が入ります。その際、「EUVで形成したパターンでは大丈夫だったが、ナノインプリントで形成したパターンだと破損が生じる」といった不具合が生じることも考えられます。ナノインプリントの利用に合わせて前後の工程のパラメータも調整する必要があるので、検証に時間がかかります。

以上、2nmプロセスの開発状況とキヤノンのナノインプリント装置の概要を解説した後、2nmプロセスにナノインプリント装置を適用する際に超えるべきハードルを整理しました。

現状のハードルを考えると、2nmプロセスの半導体チップにナノインプリント装置がすぐに使われる可能性は低そうです。ただ、ナノインプリントはEUVに比べて「装置コストの安さ」や「電力消費量の少なさ」などのメリットがあります。半導体製造における電力消費は、脱炭素化が求められる時代において深刻な課題であり、将来的にナノインプリントの普及が広がる可能性は高いと考えられます。

余談ですが、弊社代表の楠浦もナノインプリントのスタートアップを立ち上げた経験があり、半導体向けのナノインプリント開発の大変さは身に染みて理解しています。キヤノンが、シビアな精度の求められる半導体分野でナノインプリントを実用化のフェーズに到達させたのは間違いなく「偉業」であり、開発者の方々の努力には頭が下がります。

今回ご紹介した内容は、弊社の無料メールマガジンで代表の楠浦が取り上げた情報や、今後配信する予定の情報をベースに作成しています。メルマガでは技術的にさらに踏み込んだ内容や、ビジネスモデルの観点で掘り下げた考察をご紹介しております。

また、弊社の調査レポート「イノベーション四季報」では、テーマごとのイノベーション情報を総括した資料を提供しています。2022年冬号では、2nmプロセス達成に向けたTSMCやインテルの最新動向や、ナノインプリントとEUVの比較分析も解説しているので、ぜひご活用ください。

コラムや調査レポートのリリース情報もメルマガで毎週お伝えしているので、最新情報を入手する無料ツールとして是非ご活用ください。

★セミナー動画リリースのご案内

発明塾®動画セミナー『ナノインプリント・EUV比較分析セミナー ~キヤノンのナノインプリントはEUVの2nmプロセスをリプレースできるか? IRと特許情報から分析!~』

2023年12月22日(金)にご好評のうちに終了しました「キヤノンのナノインプリント装置」と「ASMLのEUV露光装置」を比較解説するセミナーを収録した動画セミナーです!

それぞれの装置の内部構造や、TSMCが2025年リリースを計画する「2nmプロセス」にナノインプリントが与える影響を、特許やIR情報を元に詳しく分析。ナノインプリント関連スタートアップでCTO経験がある弊社代表の楠浦が、実体験も交えてわかりやすく解説しています。効率よく最先端にキャッチアップしたい方はぜひご活用ください!

★本記事と関連した弊社サービス

①無料メールマガジン「e発明塾通信」

材料、医療、エネルギー、保険など幅広い業界の企業が取り組む、スジの良い新規事業をわかりやすく解説しています。半導体関連の技術に関する情報も多数発信しています。

「各企業がどんな未来に向かって進んでいるか」を具体例で理解できるので、新規事業のアイデアを出したい技術者の方だけでなく、優れた企業を見極めたい投資家の方にもご利用いただいております。週2回配信で最新情報をお届けしています。ぜひご活用ください。

②イノベーション四季報™【2022年・冬号】~半導体ビジネスを生き抜く航海図

半導体業界でキャリアアップしたい方には必見の「最新技術情報」を「ビジネス上なぜ重要か?」も含めて徹底的に解説します。本記事に関連するトピックとして、例えば「微細化が進む中でレジスト材料はどう変わるか?」「次世代トランジスタ・GAA(Gate-All-Around)の製造プロセス」を解説しています。

★弊社書籍の紹介

弊社の新規事業創出に関するノウハウ・考え方を解説した書籍『新規事業を量産する知財戦略』を絶賛発売中です!新規事業や知財戦略の考え方と、実際に特許になる発明がどう生まれるかを詳しく解説しています。

※KindleはPCやスマートフォンでも閲覧可能です。ツールをお持ちでない方は以下、ご参照ください。

Windows用 Mac用 iPhone, iPad用 Android用

畑田康司

TechnoProducer株式会社シニアリサーチャー

大阪大学大学院工学研究科 招へい教員

半導体装置の設備エンジニアとして台湾駐在、米国企業との共同開発などを経験した後、スタートアップでの事業開発を経て現職。個人発明家として「未解決の社会課題を解決する発明」を創出し、実用化・事業化する活動にも取り組んでおり、企業のアイデアコンテストでの受賞経験あり。

あらゆる業界の企業や新技術を徹底的に掘り下げたレポートの作成に定評があり、「テーマ別 深掘りコラム」と「イノベーション四季報」の執筆を担当。分野を問わずに使える発明塾の手法を駆使し、一例として以下のテーマで複数のレポートを出している。

IT / 半導体 / 脱炭素 / スマートホーム / メタバース / モビリティ / 医療 / ヘルスケア / フードテック / 航空宇宙 / スマートコンストラクション / 両利きの経営 / 知財戦略 / 知識創造理論 / アライアンス戦略

ここでしか読めない発明塾のノウハウの一部や最新情報を、無料で週2〜3回配信しております。

・あの会社はどうして不況にも強いのか?

・今、注目すべき狙い目の技術情報

・アイデア・発明を、「スジの良い」企画に仕上げる方法

・急成長企業のビジネスモデルと知財戦略